2.1.4

Explain the machine instruction cycle.

Teaching Note:

This should include the role of data bus and address bus.

Sample Questions - FORMER CURRICULUM:

4. Describe how the computer carries out a machine instruction. [4 marks]

*Abstraction Point

Remember with all of this - and this assessment statment in particular - we are trying to get a handle about how something incredibly complex works. So the level of abstraction we are at is quite high, and all of these descriptions need to be taken "with a grain of salt". The maching instruction cycle, and the various depictions of the way data and instructions move around (as in the digarams below), are not *exactly* the way things work; that is way beyond the possibilities of a course like this, But the general to-and-fro, and concepts are adequate for our level of understanding.

Machine Instruction Cycle

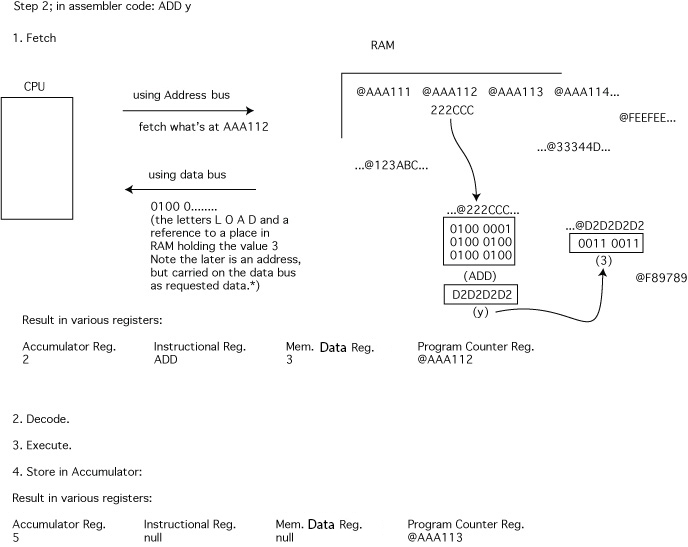

The machine instruction cycle is the steps that the CPU goes through continually to process information. At a basic level, the machine instruction cycle is typically stated as four steps:

Fetch

Decode

Execute

Store

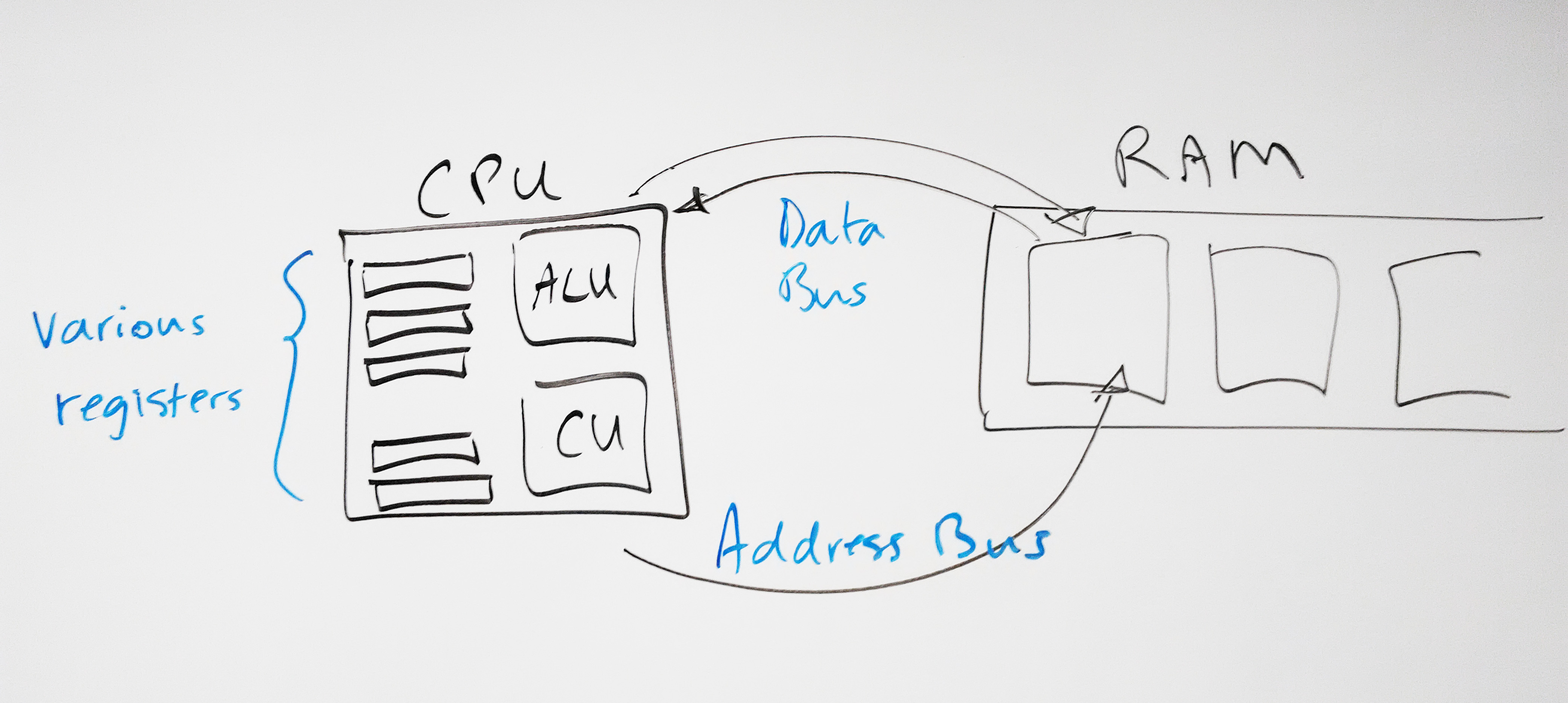

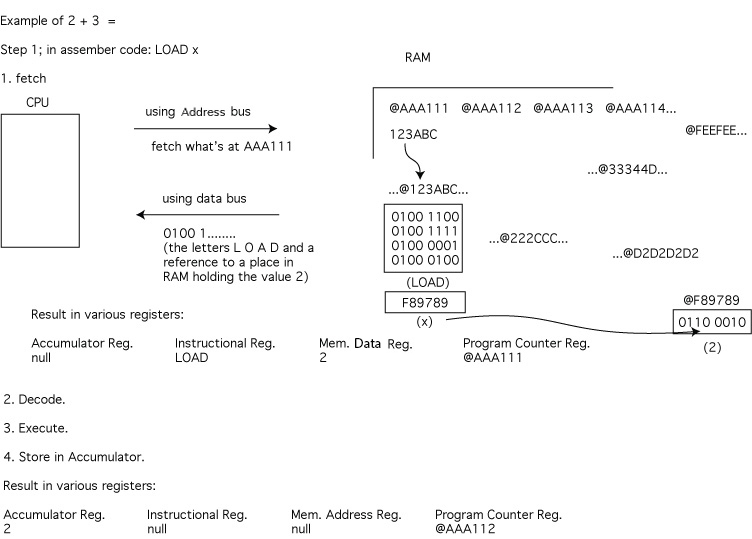

Fetch - "going to" a particular memory address in RAM to get data or instruction and bringing them back to the CPU. Knowing where to go in RAM to fetch from is compliments of the address bus being able to identify a particular location/address. The bringing back of the data or instructions is done via the data bus.

Decode - figure out what the instruction is, and how the particular CPU can execute such an instruction (such as ADD). Keep in mind, each CPU architecture has it's own way of doing things, so decoding is decoding instructions into the specifics that it can do, the way that it can do them.

Execute - that's where the Control Unit shuffles things into Arithmetic Logic Unit, the calculation is done, and the result is shuffled out of it.

Store Result - sometimes this is storing a final result to secondary storage, but usually it's just storing the partial result which has just been accomplished, such as adding a number to an ongoing calculation

Address Bus & Data Bus

From the Teaching Note point, recall that we already looked briefly at the data bus and the address bus in 2.1.1.

The term "bus" in IT refers to a certain path of wires carrying some sort of information within a certain piece of hardware, for example the system bus within the motherboard of a computer.

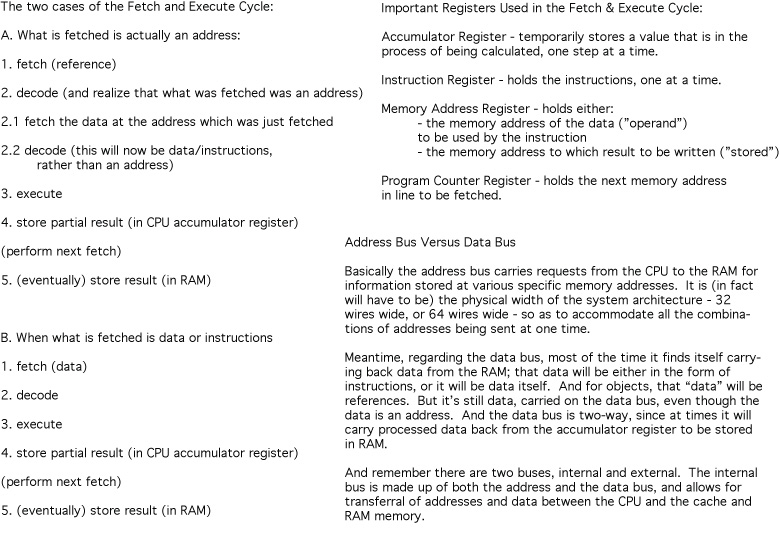

Address Bus

Recall from the diagram in 2.1.1 that the address bus is the path which the CPU uses to go to specific addresses in memory to fetch stuff from RAM and can therefore be thought of as being unidirectional. Though do note it doesn't even actually"send" data back or forth to the RAM, as the data bus does; rather, it is used by the CPU to identify particular locations in memory - to get to a certain spot in memory, to access what's there.

Data Bus

From a particular, identified RAM address, the data that is found there is returned to the CPU via the data bus. And with the data bus data can also travel back to the RAM to be saved, thereby making it a bi-directional bus. Note that the data bus is sometimes referred to as the memory bus.

A good, concise link about the address bus and the data bus. (And note that the two of these together are sometimes referred to as the memory bus system.)

And one more stab at an analogy; how about this: there are a bunch of small twisty turny streets and sidewalk shortcuts a motor bike taxi guy could use to get to just about anywhere in Bangkok. So think of him/her/them and those paths as being the address bus, sending a reqest for some data located at some specific address, which they are expert at finding. Once there, the data requested is loaded on the big lory/truck, and out to the main roads it heads, and then it takes the main highway, along with all the other trucks/lories transporting the data back and forth - i.e. on the data bus.

Fetching an Address

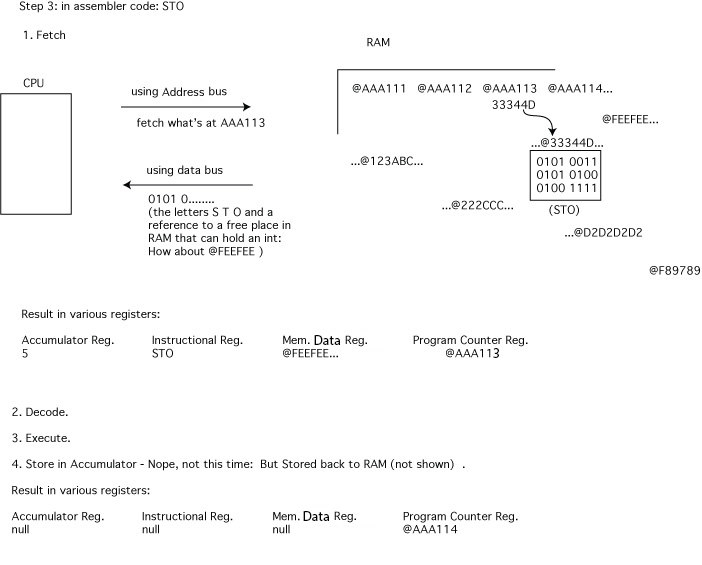

Note that it can help to include an optional step for when what is fetched is an address - which is often the case. So there are really two possibilities as the cycle cycles:

A. When what is fetched is actually an address:

- fetch (from the RAM, found via the address bus, brought back via the data bus)

- decode (and realize that what was fetched was an address)

- fetch the data at the address which was just fetched

- decode (this will now be data/instructions, rather than an address)

- execute

- store result

(perform next fetch)

B. When what is fetched is data or instructions

- fetch (from the RAM, found via the address bus, brought back via the data bus)

- decode

- execute

- store result

(perform next fetch)

The Finer Details

The above is all you really should need to know for this assessment statement. But to help you put it all together, feel free to look through the following video, and the diagrams below.

*** Note that there is a strange video editing glitch where the screen goes black for a bunch of seconds, but nothing is missed, so when it happens, at around the 6 minute mark, fast forward to around the 7:22 mark.

** And also note that the following diagrams and video are at a fairly high level of abstraction, so they are "to be taken with a grain of salt", meaning that they give general indications of how things work, without always being perfectly true to the actual functioning at a logic gate level.

A good companion to some of this would be the PBS Crash Course CS videos, in around # 5 in the series.

(JSR: Could, at this point, download a simple computer from Minecraft Redstone and mirror using it with the diagram explanation video above)

----------------

These diagrams break the fetch and execute cycle into the specifics of just what is going on.

It may be useful to keep the full CPU diagram from 2.1.1 open in a tab for reference when looking through this for the big picture. Though note that there are extra registers here, not in that diagram. But a reminder, here are a quick summary diagram:

------------

------------